课件推送(MOSFET漏源间漏电Idss浅谈-功率半导体社/功率器件应用学习笔记)

- 2026-04-03 08:29:47

课件推送(MOSFET漏源间漏电Idss浅谈-功率半导体社/功率器件应用学习笔记)继续分享课件! 这是最近困扰笔者的一个话题,翻阅了一些帖子,摘录如下: 题目:MOSFET漏源间漏电(Idss)参数浅谈 时间:2025年5月/2026年1月

全文完。

来源:功率半导体社/功率器件应用学习笔记(排名不分先后)

链接:MOSFET 源漏间漏电(IDSS)参数解读(功率半导体社)

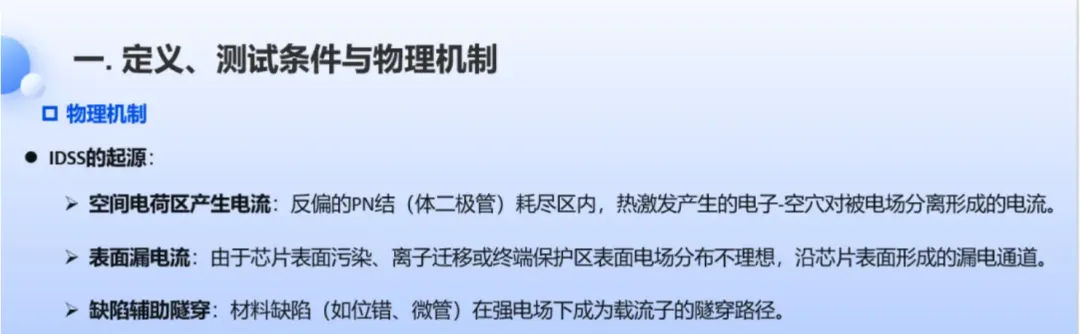

1、IDSS是指MOSFET在栅-源极短接,漏-源极之间施加指定的反向电压时(阻断状态),源漏之间流过的泄漏电流;

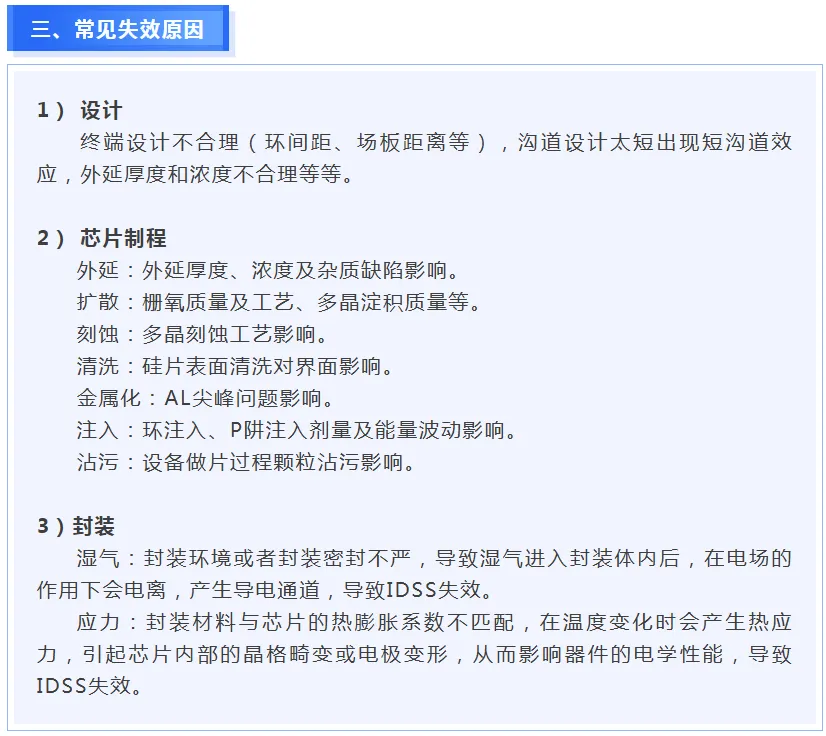

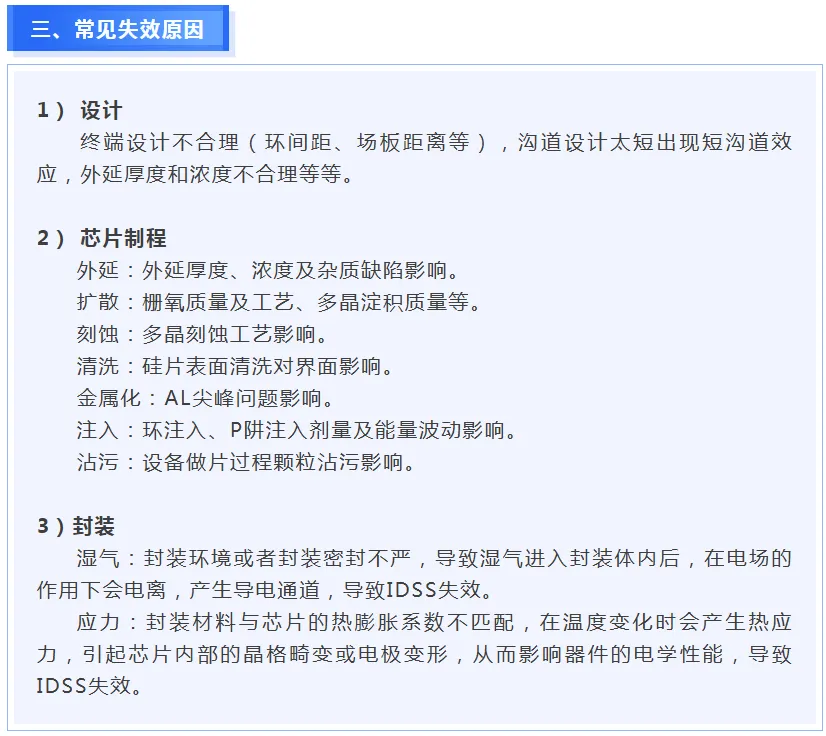

2、常见失效:

链接:SiC MOSFET规格参数中的IDSS&IGSS(功率器件应用学习笔记)

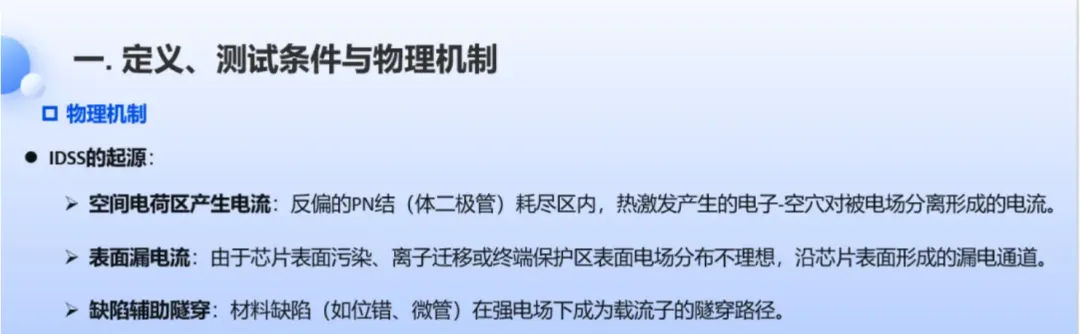

1、Idss物理机理:

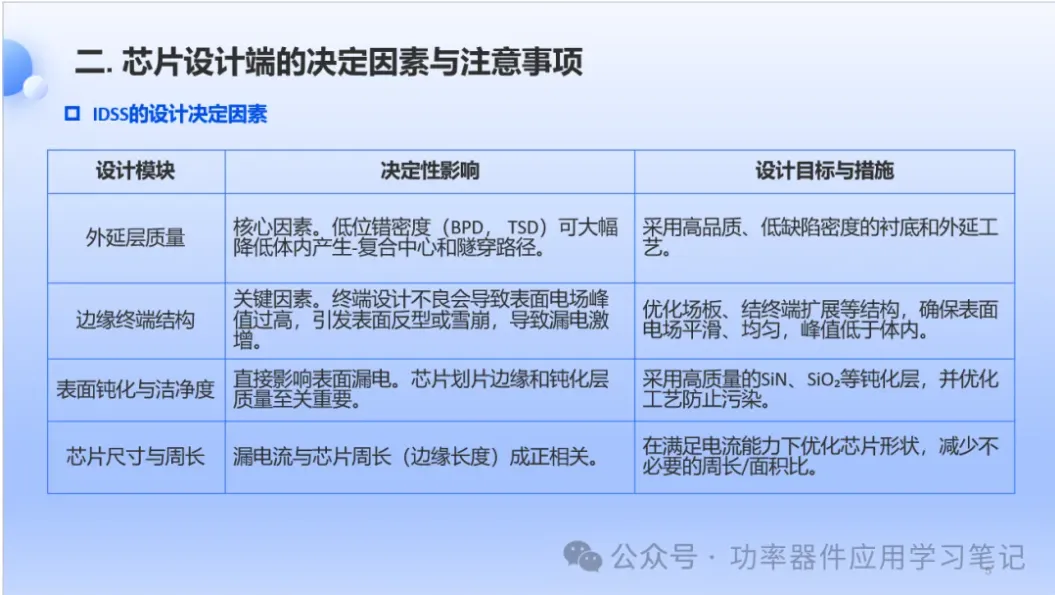

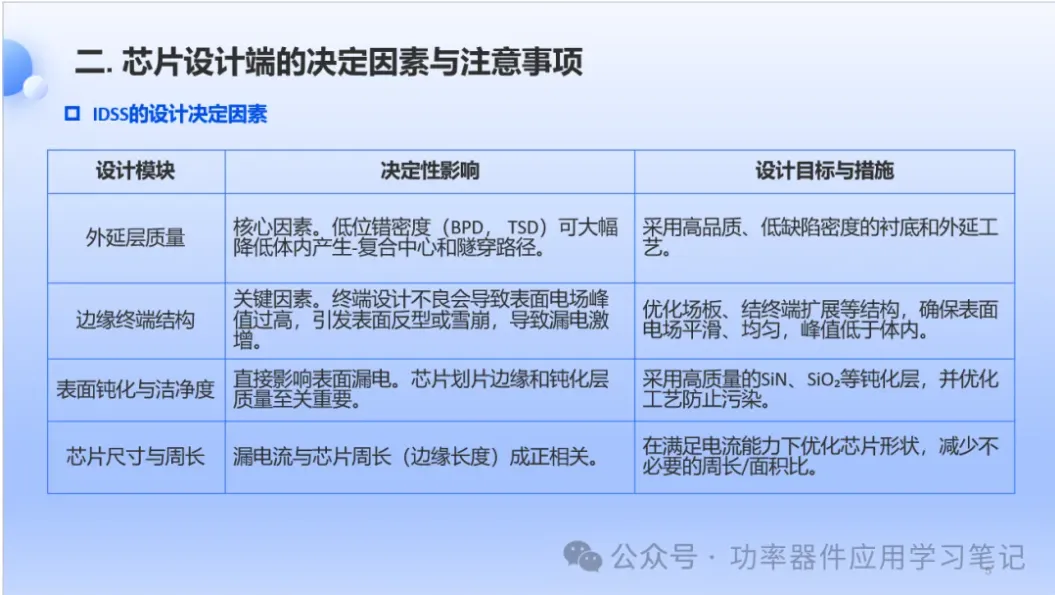

2、改善措施:芯片尺寸和周长,这点很有意思;在面积相等的所有平面图形中,圆的周长最小。

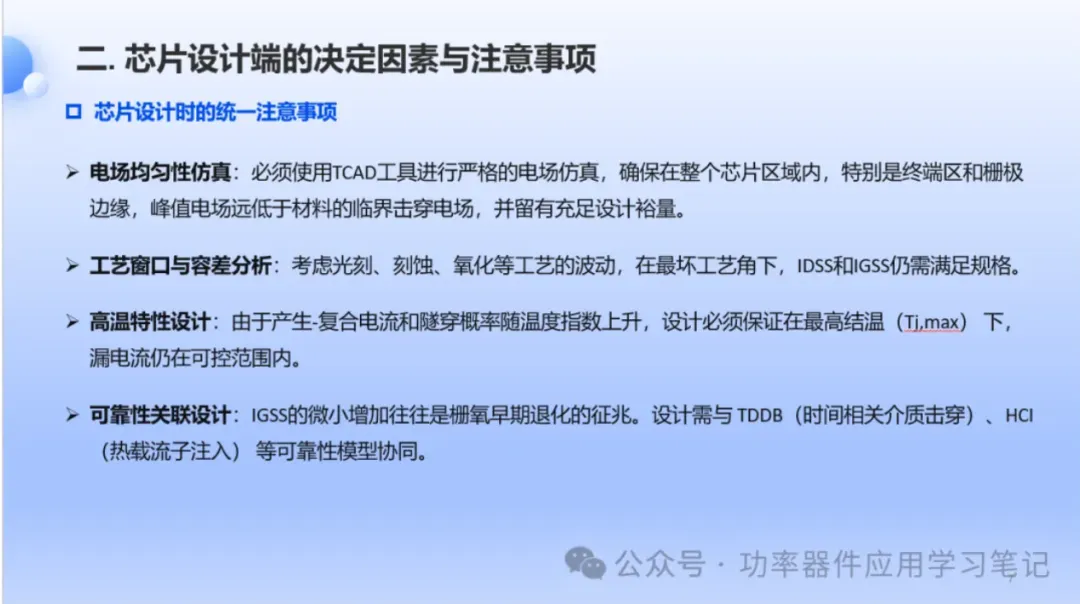

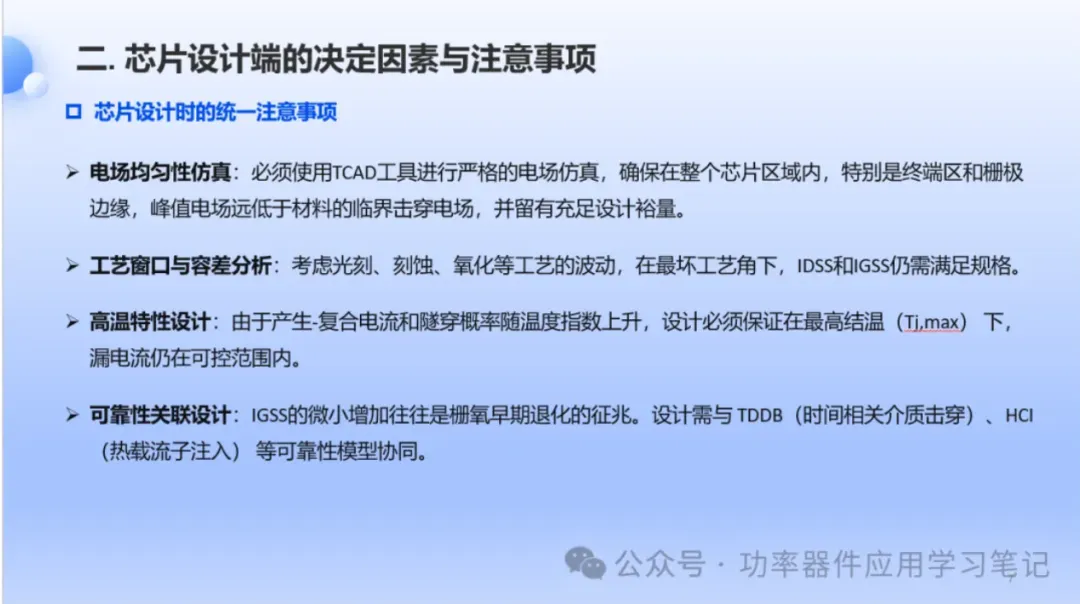

3、Idss如何进行可靠性关联设计呢?!

推荐理由:两种不同的风格,供客官们对比;MOSFET Idss漏电跟设计、工艺和封装相关,并提出了改善措施(如:优化设计(降低终端表面电场,减小芯片周长/面积比)、工艺管控(外延品质,采用高质量钝化,宽的工艺容差),封装匹配(热应力匹配,阻挡水汽/离子));还有什么好法子呢,抛砖引玉哈!!!推荐大家伙一起深究,深追追更!!!

全文完。

另功率半导体社HTRB、栅漏电(Igss)/HTGB等也有较为详尽的阐述。

本文来自网友投稿或网络内容,如有侵犯您的权益请联系我们删除,联系邮箱:wyl860211@qq.com 。